お客様の研究とOR部による解決

半導体試作前に組み込み後の製品性能評価を行いたい → シミュレーションシステムの構築

SoC(*1)設計に利用されるCASEツール(*2)の大半は、設計対象である半導体チップ単体の性能評価をシミュレーションすることは可能ですが、最終製品に組み込まれた時点での性能を 評価することはできません。そのため、最終製品の評価時に性能を満たしていないことが明らかになると、 半導体設計の再検討から始まり、時間とコストがかかります。

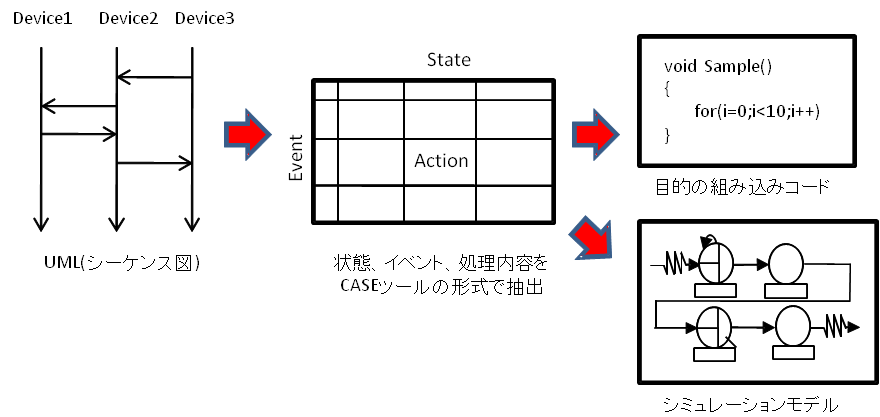

そこで私たちは、設計対象の性能を組み込んだ最終製品での様々な性能評価をシミュレーションする方法を 研究・開発しました。

設計以外の負担をできる限り減らしたい → シミュレーションモデルの自動構築を実現

SoCの設計者にとって、設計作業以外のシミュレーションモデルの開発及び試行作業は大きな負担です。私たちは、設計者の負担を最小限に抑えるため、シミュレーション条件の設定のみで様々な評価シミュレーションを実現するモデルの自動構築システムを開発しました。 これにより、設計時点での十分な性能評価が行えるようになりました。

解決までの手順

CASEツールの設計情報の解析と読み替え規則の整備

開発したシステムでは、CASEツールとして幅広く利用されている製品ZIPCを利用しました。様々なシミュレーションのモデルのパーツ(以後、モデルテンプレート)を作成し、ZIPCの書式とモデルテンプレートの対応付け規則を策定しました。これにより、ZIPCの設計情報からシミュレーションモデルが自動的に生成されるようになりました。

徹底したシミュレーションシステムの抽象化

シミュレーション実行までの操作は、シミュレーション対象の選択とシミュレーション期間の指定のみとし、 様々な設定値でのシミュレーション評価が容易に行えるようにしました。また、シミュレーションエンジンには、非常に高速で柔軟な汎用シミュレーションシステムである Visual SLAMを使用したため、より多くの評価が短時間で行えるようになります。

*1…SoC(System on a Chip)。コンピュータの主要機能であるマイクロプロセッサ、 チップセット、メモリなどの機能が1つの半導体チップに搭載されている集積回路設計手法のこと。

*2…CASEツールとは、システム設計での各種作業を支援するツールです。 設計情報からソフトウェア製品の一部(または全部)を自動生成する機能を備えるものです。

産学共同研究開発

本システム内で提供される様々な通信方式や標準的な構成の周辺機器の情報は、 上智大学 服部武教授のこれまでの研究成果に基づいてご提供頂きました。 これらのシーズに、弊社のシミュレーション技術力とシステム開発技術力を組み合わせることによって、 本システムの開発を行いました。 また、研究開発費用は独立行政法人 日本科学技術振興機構(JST)の研究助成事業 a-Step による 助成を受けて行われました。

使用製品

Visual SLAM 汎用シミュレーションモデル構築ツ―ル

学会発表

- 指尾健太郎、相澤りえ子、服部武『効率的な半導体設計のための性能評価システムの構築 ~CASEツールの設計情報に基づく シミュレーションモデル自動生成~』2010年度精密工学会春季大会, 2010年3月

- 指尾健太郎、相澤りえ子、太田洋二郎、服部武『シミュレーションによる半導体設計支援システムの構築 ~設計上流工程における 実運用環境下での性能予測~』第54回システム制御情報学会研究発表講演会,2010年5月

新聞掲載

日刊工業新聞 ,システムLSIの性能評価設計時に全体規模実験,2010年4月16日